- 您现在的位置:买卖IC网 > Sheet目录1994 > DS3106LN+ (Maxim Integrated Products)IC TIMING LINE CARD 64-LQFP

DS3106

23

7.7.1.7 Mini-Holdover

When the selected reference fails, the fast activity monitor (Section 7.5.3) isolates the T0 DPLL from the reference

within one or two clock cycles to avoid adverse effects on the DPLL frequency. When this fast isolation occurs, the

DPLL enters a temporary mini-holdover mode, with a frequency equal to an instantaneous value 50ms to 100 ms

old from the integral path of the loop filter. Mini-holdover lasts until the selected reference becomes active or the

state machine enters the holdover state. If the free-run holdover mode is set (FRUNHO = 1 in MCR3), the mini-

holdover frequency accuracy is exactly the same as the external oscillator accuracy plus the offset set by the

7.7.2 Bandwidth

The bandwidth of the T0 DPLL is configured in the T0ABW and T0LBW registers for various values from 18Hz to

400Hz. The AUTOBW bit in the MCR9 register controls automatic bandwidth selection. When AUTOBW = 1, the

T0 DPLL uses the T0ABW bandwidth during acquisition (not phase-locked) and the T0LBW bandwidth when

phase-locked. When AUTOBW = 0 the T0 DPLL uses the T0LBW bandwidth all the time, both during acquisition

and when phase-locked.

When LIMINT = 1 in the MCR9 register, the DPLL’s integral path is limited (i.e., frozen) when the DPLL reaches

minimum or maximum frequency. Setting LIMINT = 1 minimizes overshoot when the DPLL is pulling in.

7.7.3 Damping Factor

The damping factor for the T0 DPLL is configured in the DAMP field of the T0CR2 register. The reset default

damping factor is chosen to give a maximum jitter/wander gain peak of approximately 0.1dB. Available settings are

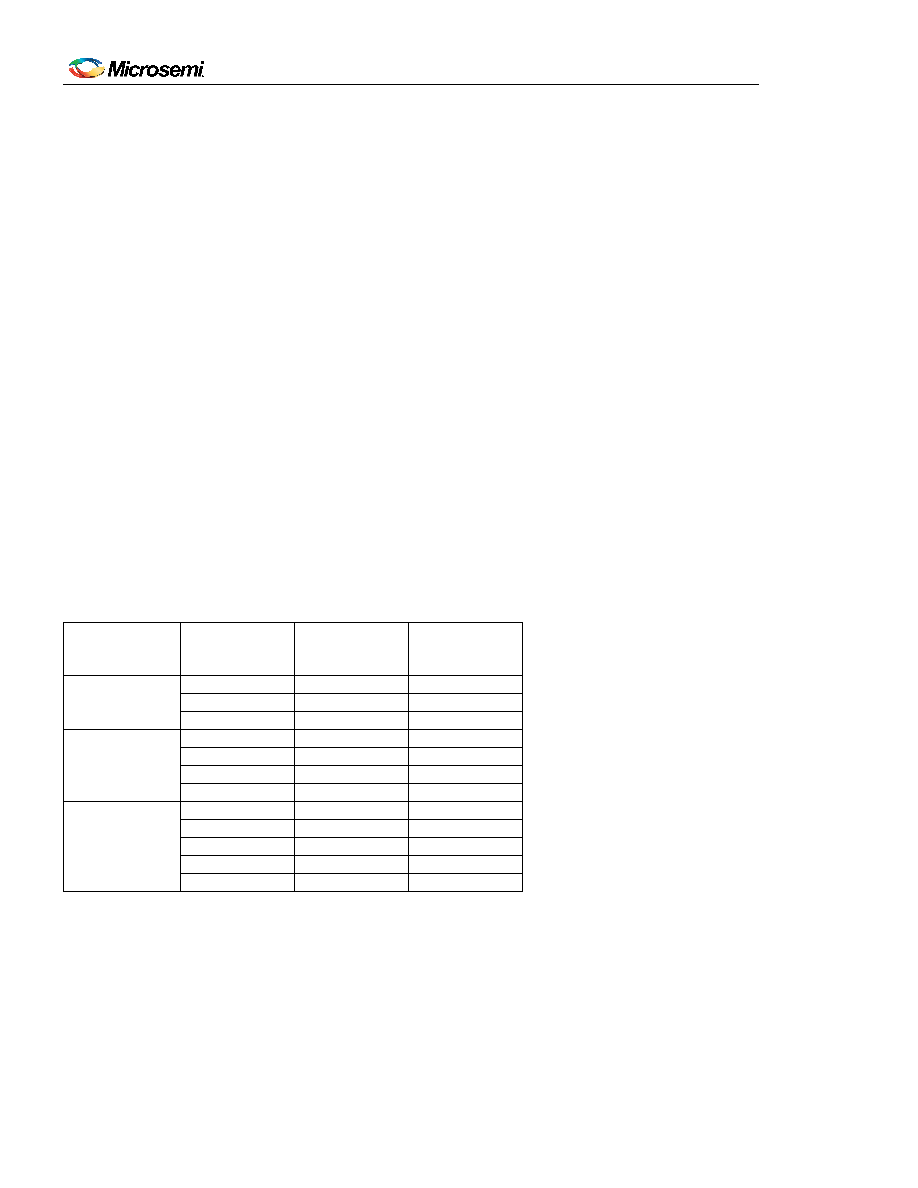

Table 7-4. Damping Factors and Peak Jitter/Wander Gain

BANDWIDTH

(Hz)

DAMP[2:0]

VALUE

DAMPING

FACTOR

GAIN PEAK

(dB)

18

1

1.2

0.4

2

2.5

0.2

3, 4, 5

5

0.1

35

1

1.2

0.4

2

2.5

0.2

3

5

0.1

4, 5

10

0.06

70 to 400

1

1.2

0.4

2

2.5

0.2

3

5

0.1

4

10

0.06

5

20

0.03

7.7.4 Phase Detectors

Phase detectors are used to compare a PLL’s feedback clock with its input clock. Several phase detectors are

available in the T0 DPLL:

Phase/frequency detector (PFD)

Early/late phase detector (PD2) for fine resolution

Multicycle phase detector (MCPD) for large input jitter tolerance and/or faster lock times

These detectors can be used in combination to give fine phase resolution combined with large jitter tolerance. As

with the rest of the DPLL logic, the phase detectors operate at input frequencies up to 77.76MHz. The multicycle

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DS3231MZ+

IC RTC I2C 8SOIC

DS3231SN#T&R

IC RTC W/TCXO 16-SOIC

DS3232MZ+

IC RTC W/SRAM I2C 8SOIC

DS3232SN#T&R

IC RTC W/TCXO 20-SOIC

DS3234S#

IC RTC W/TCXO 20-SOIC

DS32C35-33#T&R

IC RTC ACCURATE I2C 3.3V 20-SOIC

DS3911T+

IC DAC 10BIT I2C QUAD 14TDFN

DS4000KI/WBGA

IC OSC TCXO 19.44MHZ 24-BGA

相关代理商/技术参数

DS3107FP000

制造商:Thomas & Betts 功能描述:30A,CON,2P3W,MG,107,125V

DS3107FRAB0

制造商:Thomas & Betts 功能描述:30A,REC,2P3W,MG,107,AB0,125,SC

DS3107MP000

制造商:Thomas & Betts 功能描述:30A,PLG,2P3W,MG,107,125V

DS3107MP00K

制造商:Thomas & Betts 功能描述:30A,PLG,2P3W,MG,107,125V,CC

DS3107MR000

制造商:Thomas & Betts 功能描述:30A,NLT,2P3W,MG,107,125V

DS3107MRAB0

制造商:Thomas & Betts 功能描述:30A,NLT,2P3W,MG,107,AB0,125V

DS3108A14S5S621

制造商:Amphenol Corporation 功能描述:

DS3108A14S6S

制造商:Amphenol Corporation 功能描述: